Product Summary

The as7c331mpfs18a-166tqc is a 3.3V 1M x 18 pipelined burst synchronous SRAM. The as7c331mpfs18a-166tqc is organized as 1,048,576 words X 18 bits and incorporates a two-stage register-register pipeline for highest frequency on any given technology. Fast cycle times of 6/7.5 ns of the as7c331mpfs18a-166tqc with clock access times (tCD) of 3.4/3.8 ns enable 166, and 133 MHz bus frequencies. The as7c331mpfs18a-166tqc operates from a core 3.3V power supply I/Os use a separate power supply that can operate at 2.5V or 3.3V. The as7c331mpfs18a-166tqc is available in a 100-pin TQFP package.

Parametrics

as7c331mpfs18a-166tqc absolute maximum ratings: (1) Power supply voltage relative to GND VDD, VDDQ: -0.5 to +4.6V; (2) Input voltage relative to GND (input pins) VIN: -0.5 to VDD +0.5V; (3) Input voltage relative to GND (I/O pins) VIN: -0.5 to VDDQ +0.5V; (4) Power dissipation PD: 1.8W; (5) DC output current IOUT: 20mA; (6) Storage temperature Tstg: -65 to 150°C; (7) Temperature under bias Tbias: -65 to +150°C.

Features

as7c331mpfs18a-166tqc features: (1) Organization: 1,048,576 x18 bits; (2) Fast clock speeds to 166MHz; (3) Fast clock to data access: 3.4/3.8 ns; (4) Fast OE access time: 3.4/3.8 ns; (5) Fully synchronous register-to-register operation; (6) Single-cycle deselect; (7) Asynchronous output enable control; (8) Available 100-pin TQFP package; (9) Individual byte write and global write; (10) Multiple chip enables for easy expansion; (11) 3.3 V core power supply; (12) 2.5 V or 3.3V I/O operation with separate VDDQ; (13) Linear or interleaved burst control; (14) Common data inputs and data outputs; (15) Snooze mode for reduced power-standby.

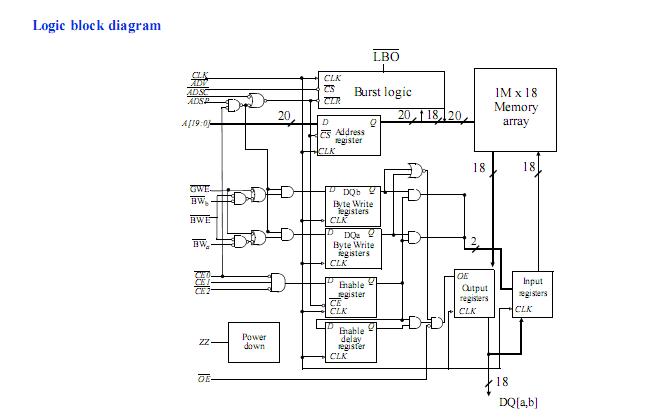

Diagrams

(Hong Kong)

(Hong Kong)