Product Summary

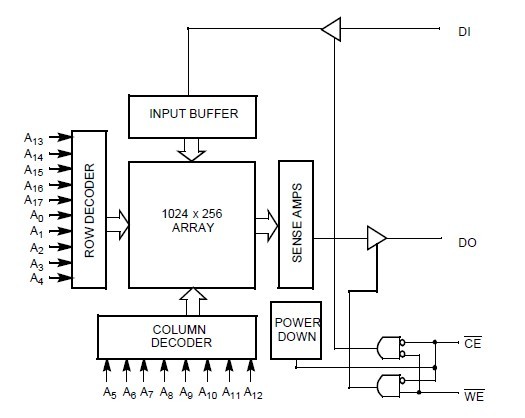

The CY62127VLL-70ZI is a high-performance CMOS Static RAM organized as 65,536 words by 16 bits. The CY62127VLL-70ZI has an automatic power-down feature that significantly reduces power consumption by 99% when deselected. The CY62127VLL-70ZI enters power-down mode when CE is HIGH or when CE is LOW and both BLE and BHE are HIGH. The input/output pins (I/O1 through I/O16) are placed in a high-impedance state when the device is deselected (CE HIGH), the outputs are disabled (OE HIGH), the BHE and BLE are disabled (BHE, BLE HIGH), or during a write operation (CE LOW, and WE LOW). The CY62127VLL-70ZI is available in standard 44-pin TSOP Type II (forward pinout) and fBGA packages.

Parametrics

CY62127VLL-70ZI absolute maximum ratings: (1)Storage Temperature : –65°C to +150°C; (2)Ambient Temperature with Power Applied: –55°C to +125°C; (3)Supply Voltage on VCC to Relative GND[1] : –0.5V to +4.6V; (4)DC Voltage Applied to Outputs in High Z State[1] : –0.5V to VCC + 0.5V; (5)DC Input Voltage[1] : –0.5V to VCC + 0.5V; (6)Current into Outputs (LOW): 20 mA; (7)Static Discharge Voltage : >2001V; (8)Latch-Up Current: >200 mA.

Features

CY62127VLL-70ZI features: (1)2.7V–3.6V operation; (2)CMOS for optimum speed/power; (3)Low active power (70 ns, LL version): 54 mW (max.)(15 mA); (4)Low standby power (70 ns, LL version): 54 μW (max.)(15 μA); (5)Automatic power-down when deselected: Power down either with CE or BHE and BLE HIGH; (6)Independent control of Upper and Lower Bytes; (7)Available in 44-pin TSOP II (forward)and fBGA.

Diagrams

(Hong Kong)

(Hong Kong)