Product Summary

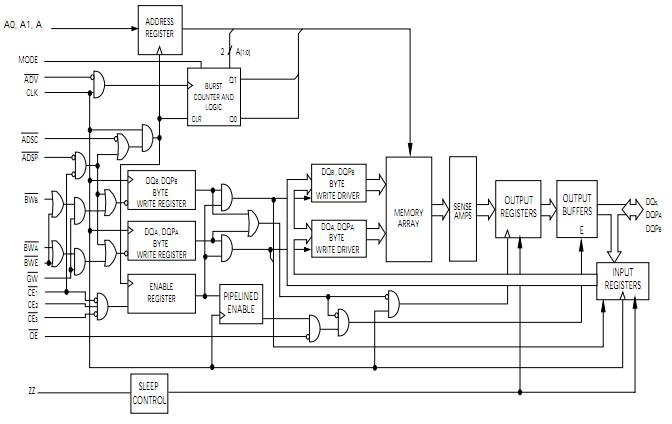

The CY7C1328A-133AI is a 4-Mb (256K × 18) Pipelined DCD Sync SRAM. The CY7C1328A-133AI integrates 262,144 × 18 SRAM cells with advanced synchronous peripheral circuitry and a two-bit counter for internal burst operation. All synchronous inputs of the CY7C1328A-133AI are gated by registers controlled by a positive-edge-triggered Clock Input (CLK). The synchronous inputs of the CY7C1328A-133AI include all addresses, all data inputs, address-pipelining Chip Enable (CE1), depth-expansion Chip Enables (CE2 and CE3), Burst Control inputs (ADSC, ADSP, and ADV), Write Enables (BW[A:B], and BWE), and Global Write (GW). Asynchronous inputs of the CY7C1328A-133AI include the Output Enable (OE) and the ZZ pin.

Parametrics

CY7C1328A-133AI absolute maximum ratings: (1)Storage Temperature: –65 to +150 ℃; (2)Ambient Temperature with Power Applied: –55 to +125 ℃; (3)Supply Voltage on VCC to Relative GND[2]: –0.5 V to +4.6 V; (4)DC Voltage Applied to Outputs[2] in High Z State: –0.5 V to VCC + 0.5 V; (5)DC Input Voltage[2]: –0.5 V to VCC + 0.5 V; (6)Current into Outputs (LOW): 20 mA; (7)Static Discharge Voltage: >2001V; (8)Latch-Up Current: >200 mA.

Features

CY7C1328A-133AI features: (1)Registered inputs and outputs for pipelined operation; (2)Optimal for performance (Double-Cycle deselect); (3)Depth expansion without wait state; (4)256K × 18-bit common I/O architecture; (5)3.3V –5% and +10% core power supply (VDD); (6)3.3V / 2.5V I/O supply (VDDQ); (7)Fast clock-to-output times; (8)Provide high-performance 3-1-1-1 access rate; (9)User-selectable burst counter supporting Intel Pentium interleaved or linear burst sequences; (10)Separate processor and controller address strobes; (11)Synchronous self-timed writes; (12)Asynchronous Output Enable; (13)JEDEC-standard 100-pin TQFP package and pinout; (14)“ZZ” Sleep Mode option.

Diagrams

(Hong Kong)

(Hong Kong)