Product Summary

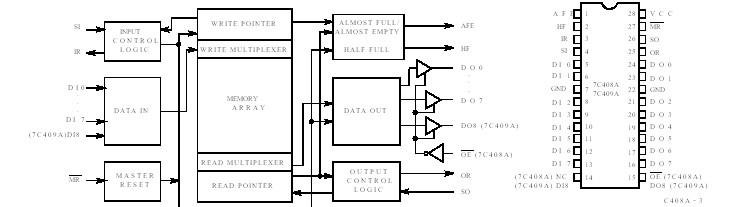

The CY7C408A-25VI is a 64-word deep by 8- or 9-bit wide first-in first-out (FIFO) buffer memory. In additionto the industry-standard handshaking signals, almost full/al-most empty (AFE) and half-full (HF) flags are provided. AFE of the CY7C408A-25VI is HIGH when the FIFO is almost full or almost empty, otherwise AFE is LOW. HF is HIGH when the FIFO is half full,otherwise HF is LOW. The CY7C408A-25VI has an output enable (OE) function. The CY7C408A-25VI accepts 8- or 9-bit parallel words as its inputs (DI0– DI8) under the control of the shift in (SI) input when the inputready (IR) control signal is HIGH. The data of is output, in thesame order as the CY7C408A-25VI was stored on the DO0 – DO8 output pinsunder the control of the shift out (SO) input when the outputready (OR) control signal is HIGH. If the FIFO of the CY7C408A-25VI is full (IR LOW),pulses at the SI input are ignored; if the FIFO is empty (ORLOW), pulses at the SO input are ignored.

Parametrics

CY7C408A-25VI absolute maximum ratings: (1)Storage Temperature: –65 to +150 ℃; (2)Ambient Temperature with Power Applied: –55 to +125 ℃; (3)Supply Voltage to ground potential: –0.5 V to +7.0 V; (4)DC Voltage Applied to Outputs in High Z State: –0.5 V to 7.0 V; (5)DC Input Voltage: –0.5 V to 7.0 V; (6)Power dissipation: 1.0 W; (7)Output Current into Outputs (LOW): 20 mA; (8)Static Discharge Voltage: >2001V.

Features

CY7C408A-25VI features: (1)64 × 8 and 64 × 9 first-in first-out (FIFO) buffer memory; (2)35-MHz shift in and shift out rates; (3)Almost Full/Almost Empty and Half Full flags; (4)Dual-port RAM architecture Fast (50-ns) bubble-through; (5)Independent asynchronous inputs and outputs; (6)Output enable; (7)Expandable in word width and FIFO depth; (8)5V± 10% supply; (9)TTL complete; (10)Capable of withstanding greater than 2001V electro-static discharge voltage; (11)300-mil, 28-pin DIP.

Diagrams

(Hong Kong)

(Hong Kong)