Product Summary

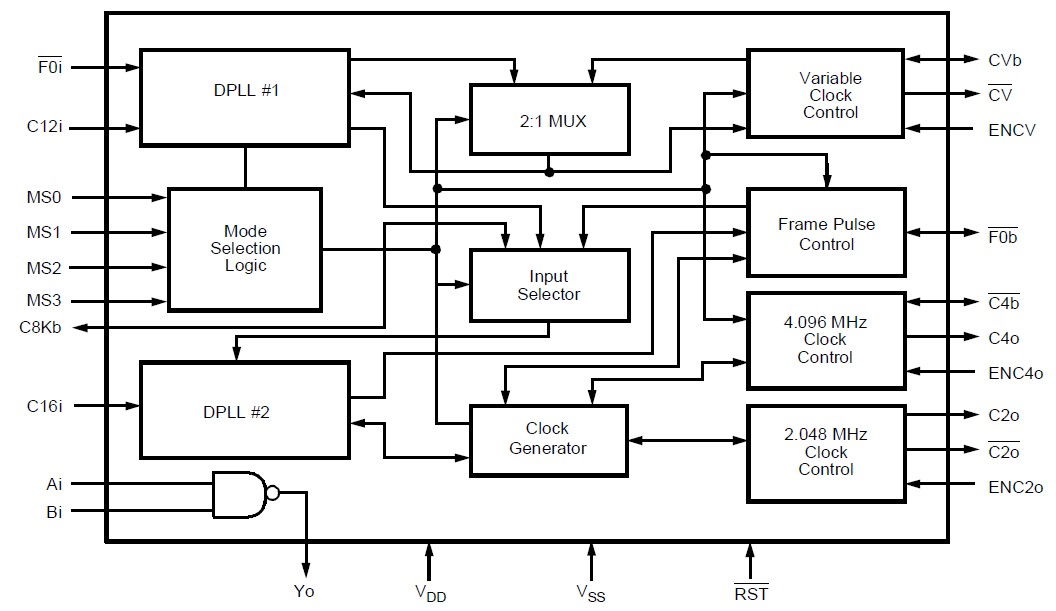

The MT8941AE is a dual digital phase-locked loop providing the timing and synchronization signals for the T1 or CEPT transmission links and the ST-BUS. The first PLL provides the T1 clock (1.544 MHz)synchronized to the input frame pulse at 8 kHz. The timing signals for the CEPT transmission link and the ST-BUS are provided by the second PLL locked to an internal or an external 8 kHz frame pulse signal. The applications of the MT8941AE include: (1)Synchronization and timing control for T1 and CEPT digital trunk transmission links; (2)ST- BUS clock and frame pulse source.

Parametrics

MT8941AE absolute maximum ratings: (1)Supply Voltage VDD: -0.3 to 7.0 V; (2)Voltage on any pin VI: VSS-0.3 to VDD+0.3 V; (3)Input/Output Diode Current IIK/OK: ±10 mA; (4)Output Source or Sink Current IO: ±25 mA; (5)DC Supply or Ground Current IDD/ISS: ±50 mA; (6)Storage Temperature TST: -55 to 125 ℃; (7)Package Power Dissipation Plastic DIP PD: 1200mW; PLCC PD: 600mW.

Features

MT8941AE features: (1)Provides T1 clock at 1.544 MHz locked to an 8 kHz reference clock (frame pulse); (2)Provides CEPT clock at 2.048 MHz and STBUS clock and timing signals locked to an internal or external 8 kHz reference clock; (3)Typical inherent output jitter (unfiltered)= 0.07 UI peak-to-peak; (4)Typicaljitter attenuation at: 10 Hz=23 dB, 100Hz=43 dB, 5 to 40 kHz ≥64 dB; (5)Jitter-free FREE-RUN mode; (6)Uncommitted two-input NAND gate; (7)Low power CMOS technology.

Diagrams

|

MT8910-1 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

MT8920B |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

MT8920BE |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

MT8924 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

MT8924AE |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

MT8926 |

Other |

|

Data Sheet |

Negotiable |

|

||||

(Hong Kong)

(Hong Kong)