Product Summary

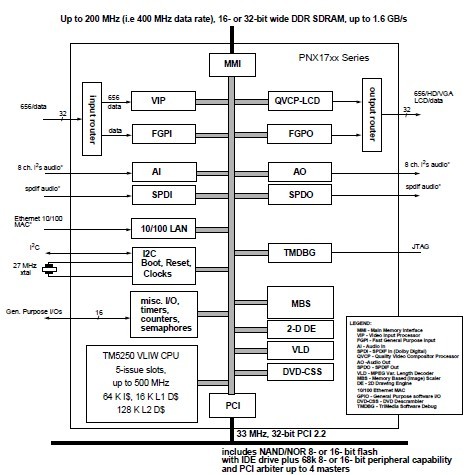

The PNX1701EH/G is a Media Processor. The PNX1701EH/G is complete Audio/Video/Graphics system on a chip that contains a high-performance 32-bit VLIW processor, capable of software High Definition video and audio signal processing, as well as general purpose control processing. It is capable of running a pSOS operating system with real-time signal processing tasks in a single programming and task scheduling environment. An abundance of interfaces make the PNX1701EH/G suitable for networked audio/visual products. The processor is assisted by several image and video processing accelerators that support image scaling and compositing.

Parametrics

PNX1701EH/G absolute maximum ratings: (1)V CCP 3.3 V I/O supply voltage: -0.5 to 4.6 V; (2)V CCM SSTL DDR-I I/O supply voltage: -0.5 to 3.6 V; (3)V DD SoC Core supply voltage: -0.5 to 1.7 V; (4)V ICCP Input voltage for 5 V tolerant input pins (i.e. pins supplied by V CCP): -0.5 to 6.0 V; (5)Tstg Storage temperature range: -65 to 150 °C; (6)TJmax Operating junction temperature range: 0 to 125 °C; (7)HBMESD Human Body Model Electrostatic handling for all pins: 2000 V; (8)MMESD Machine Model Electrostatic handling for all pins: 100 V.

Features

PNX1701EH/G features: (1)A limited number of native pixel formats are supported by all image subsystems, as appropriate; (2)The Memory Based Scaler supports conversion from arbitrary pixel formats to any native format during the anti-flicker filtering operation. This operation is usually required on graphics images anyway, hence no extra passes are introduced; (3)Hardware subsystems support all native pixel formats in both little-endian and big-endian system operation; (4)Software always sees the same component layout for a native pixel format unit, whether it is running in little-endian or big-endian mode. i.e. for a given native format, R, G, B (or Y,U,V)and alpha are always in the same place; (5)Software (on the TM5250 CPU)can be written endian-mode independent, even when doing SIMD style vectorized computations; (6)an external wake-up event on pin GPIO[15]. When entering in sleep mode, the GPIO[15] pin state (i.e. value of the pin)is sampled and registered. The CPU is woken up if the pin GPIO[15] changes state (from low to high)after the system has gone into sleep mode. The GPIO[15] pin is observable by software; (7)an expired internal counter. Before entering in sleep mode, this special counter is set up to count XTAL_IN clock ticks. Once the count is satisfied, the CPU is woken up. The counter has 32 bits.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||

|---|---|---|---|---|---|---|---|---|---|---|

|

PNX1701EH/G |

NXP Semiconductors |

Digital Signal Processors & Controllers (DSP, DSC) MEDIA PROCESSOR PNX17XX/450MHZ |

Data Sheet |

Negotiable |

|

||||

|

PNX1701EH/G,557 |

NXP Semiconductors |

Digital Signal Processors & Controllers (DSP, DSC) MEDIA PROCESSOR |

Data Sheet |

Negotiable |

|

||||

(Hong Kong)

(Hong Kong)