Product Summary

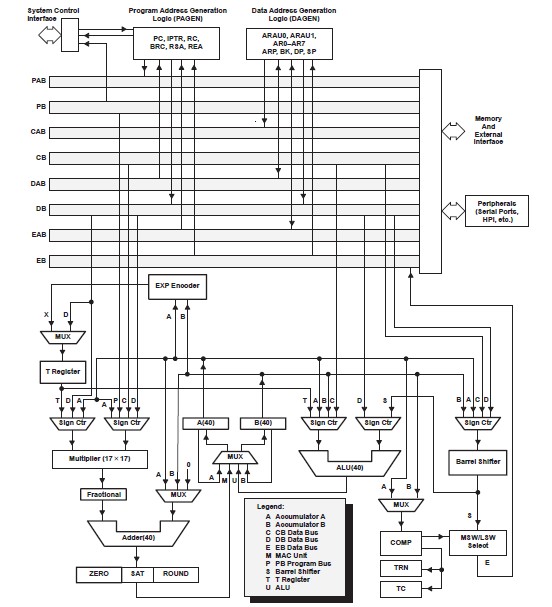

The TMS320LC548GUU-75 is a fixed-point, digital signal processor (DSP) (hereafter referred to as the 54x unless otherwise specified) is based on an advanced modified Harvard architecture that has one program memory bus and three data memory buses. The TMS320LC548GUU-75 also provide an arithmetic logic unit (ALU) that has a high degree of parallelism, application-specific hardware logic, on-chip memory, and additional on-chip peripherals. The TMS320LC548GUU-75 also provide a highly specialized instruction set, which is the basis of the operational flexibility and speed of these DSPs.

Parametrics

TMS320LC548GUU-75 absolute maximum ratings: (1)Supply voltage range, VDD: –0.3 V to 7 V; (2)Input voltage range: –0.3 V to 7 V; (3)Output voltage range: –0.3 V to 7 V; (4)Operating case temperature range, TC: –40°C to 100°C; (5)Storage temperature range, Tstg: –55°C to 150°C; (6)IOH High-level output current: –300 mA; (7)IOL Low-level output current: 2 mA.

Features

TMS320LC548GUU-75 features: (1)On-Chip ROM with Some Configurable to Program/Data Memory; (2)Dual-Access On-Chip RAM; (3)Single-Access On-Chip RAM; (4)Single-Instruction Repeat and Block-Repeat Operations for Program Code; (5)Block-Memory-Move Instructions for Better Program and Data Management; (6)Instructions With a 32-Bit Long Word Operand; (7)Instructions With Two- or Three-Operand Reads; (8)Arithmetic Instructions With Parallel Store and Parallel Load; (9)Compare, Select, and Store Unit (CSSU)for the Add/Compare Selection of the Viterbi Operator; (10)Exponent Encoder to Compute an Exponent Value of a 40-Bit Accumulator Value in a Single Cycle; (11)Two Address Generators With Eight Auxiliary Registers and Two Auxiliary Register Arithmetic Units (ARAUs); (12)Data Bus With a Bus Holder Feature.

Diagrams

(Hong Kong)

(Hong Kong)