Product Summary

The TNETV3010DGVC transport mode (ATM) line-interface receiver/transmitter provides a single-chip implementation for transporting ATM cells over the SONET/SDH network at the STS-3c/STM-1 rate of 155.52 Mbits/s. The TNETV3010DGVC provides all the functionality required to insert and extract 53-byte ATM cells into/from an STS-3c/STM-1 synchronous payload envelope (SPE), including clock recovery and clock generation using analog phase-locked loops (APLL).

Parametrics

TNETV3010DGVC absolute maximum ratings: (1)Supply voltage range, VCC (see Note 1): TTL: –0.5 V to 7 V, PECL: –0.5 V to 7 V; (2)Analog supply voltage range, AVCC: –0.5 V to 7 V; (3)Input voltage range, VI TTL: –1.2 V to 7 V, PECL: 0 V to PVCC; (4)Operating free-air temperature range, TA: 0°C to 70°C; (5)Storage temperature range, Tstg: –65°C to 150°C; (6)II Input current TTL VCC = 5.25 V, VI = VCC or GND: ±300 mA; (7)Ci Input capacitance TTL: 4 pF.

Features

TNETV3010DGVC features: (1)SingleChip Receiver/Transmitter for Transporting 53Byte Asynchronous Transport Mode (ATM)Cells Via STS3c/STM1 Frame (155.52 Mbit/s); (2)OnChip Analog PhaseLocked Loop (APLL)Provides; (3)Inserts and Extracts ATM Cells Into/From SONET/SDH STS3c/STM1 SPE; (4)Detects MultipleBit Errors and Corrects SingleBit Errors in the 5Byte ATM Headers of Incoming ATM Cells; (5)Loss of Incoming Serial Signal (LOS); (6)Out of Frame (OOF); (7)Loss of Frame (LOF); (8)B1Byte Parity Error (B1ERR); (9)Loss of ATM Cell Alignment (LOCA); (10)Line FarEnd Receive Failure (LFERF); (11)Receive Loss of Pointer (LOP); (12)Line Alarm Indication Signal (LAIS); (13)Meets ATM Forum ATM UserNetwork Interface Specification Requirement; (14)Package Options Include 144Pin Plastic Quad Flat (PCM)and 144Pin Thin Quad Flat (PGE)Packages.

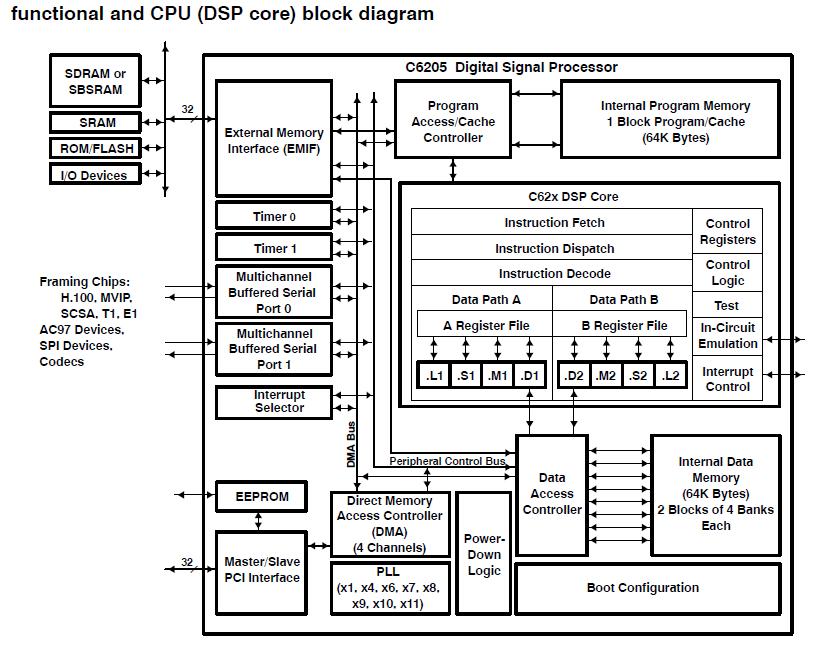

Diagrams

(Hong Kong)

(Hong Kong)