Product Summary

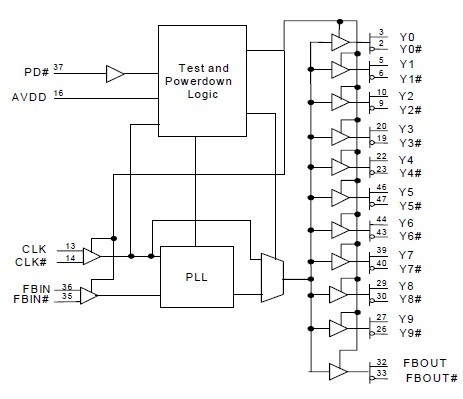

The CY2SSTV857ZXC-27T is a high-performance, low-skew, low-jitter zero-delay buffer designed to distribute differential clocks in high-speed applications. The CY2SSTV857ZXC-27T generates ten differential pair clock outputs from one differential pair clock input. In addition, the CY2SSTV857ZXC-27T features differential feedback clock outputs and inputs. This allows the CY2SSTV857ZXC-27T to be used as a zero-delay buffer. When used as a zero-delay buffer in nested clock trees, the CY2SSTV857ZXC-27T locks onto the input reference and translates with near-zero delay to low-skew outputs.

Parametrics

CY2SSTV857ZXC-27T absolute maximum ratings: (1)Input Voltage Relative to VSS: VSS – 0.3V; (2)Input Voltage Relative to VDDQ or AVDD: VDDQ + 0.3V; (3)Storage Temperature:–65°C to + 150°C; (4)Operating Temperature: 0°C to +85°C; (5)Maximum Power Supply: 3.5V; (6)IIN Input Current [CLK, FBIN, PD#] VIN = 0V or VIN = VDDQ: –10 to 10 μA; (7)fCLK Operating Clock Frequency AVDD, VDDQ = 2.5V ± 0.2V: 60 to 200 MHz.

Features

CY2SSTV857ZXC-27T features: (1)Operating frequency: 60 MHz to 200 MHz; (2)Supports 266, 333-MHz DDR SDRAM; (3)10 differential outputs from 1 differential input; (4)Spread-Spectrum-compatible; (5)Low jitter (cycle-to-cycle): < 75; (6)Very low skew: < 100 ps; (7)Power management control input; (8)High-impedance outputs when input clock < 10 MHz; (9)2.5V operation; (10)Pin-compatible with CDC857-2 and -3; (11)48-pin TSSOP package; (12)Industrial temp. of –40° to +85°C; (13)Conforms to JEDEC DDR specification.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

CY2SSTV857ZXC-27T |

Silicon Labs |

Clock Buffer 2.5V 60-200MHz 1:10 Diff DDR266/333 B/D |

Data Sheet |

|

|

||||||||||||

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||

|

CY2SSTU32864 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||

|

CY2SSTU877 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||

|

CY2SSTV16857 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||

|

CY2SSTV16859 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||

|

CY2SSTV850ZC |

Silicon Labs |

Clock Buffer 2.5V 170MHz 1:10 Diff DDR PLL+I2C |

Data Sheet |

|

|

||||||||||||

|

CY2SSTV850ZCT |

Silicon Labs |

Clock Buffer 2.5V 170MHz 1:10 Diff DDR PLL+I2C |

Data Sheet |

|

|

||||||||||||

(Hong Kong)

(Hong Kong)