Product Summary

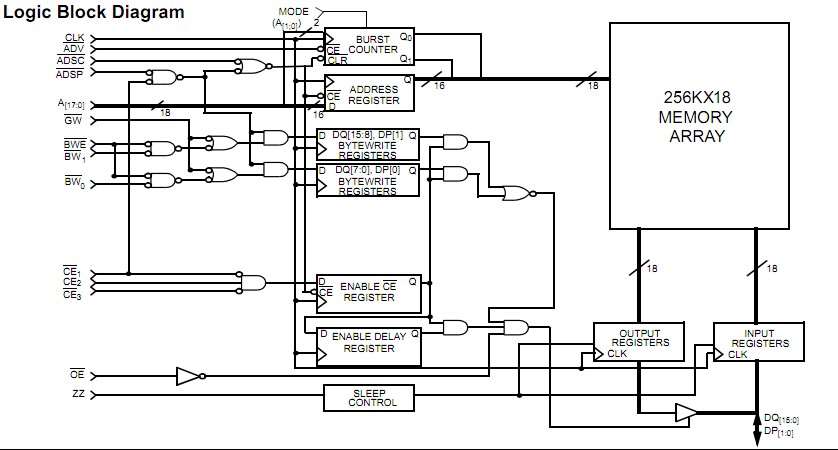

The CY7C1327B-100AI is a 3.3V, 256K by 18 synchronous-pipelined cache SRAM designed to support zero wait state secondary cache with minimal glue logic. The CY7C1327B-100AI pins can operate at either the 2.5V or the 3.3V level. The I/O pins of the CY7C1327B-100AI are 3.3V tolerant when VDDQ=2.5V. All synchronous inputs pass through input registers controlled by the rising edge of the clock. All data outputs pass through output registers controlled by the rising edge of the clock. Max-imum access delay from the clock rise is 3.5 ns (166-MHz device). The CY7C1327B-100AI supports either the interleaved burst sequence used by the Intel Pentium processor or a linear burst sequence used by processors such as the PowerPC.

Parametrics

CY7C1327B-100AI absolute maximum ratings: (1)Storage Temperature: –65 to +150 ℃; (2)Ambient Temperature with Power Applied: –55 to +125 ℃; (3)Supply Voltage on VCC to Relative GND[2]: –0.5 V to +4.6 V; (4)DC Voltage Applied to Outputs[2] in High Z State: –0.5 V to VCC + 0.5 V; (5)DC Input Voltage[2]: –0.5 V to VCC + 0.5 V; (6)Current into Outputs (LOW): 20 mA; (7)Static Discharge Voltage: >2001V; (8)Latch-Up Current: >200 mA.

Features

CY7C1327B-100AI features: (1)Supports 100-MHz bus for Pentium and PowerPC operations with zero wait states; (2)Fully registered inputs and outputs for pipelined operation; (3)256K by 18 common I/O architecture; (4)3.3V core power supply; (5)2.5V / 3.3V I/O operation; (6)Fast clock-to-output times; (7)User-selectable burst counter supporting Intel Pentium interleaved or linear burst sequences; (8)Separate processor and controller address strobes; (9)Synchronous self-timed writes; (10)Asynchronous Output Enable; (11)JEDEC-standard 100 TQFP pinout; (12)“ZZ” Sleep Mode option and Stop Clock option.

Diagrams

(Hong Kong)

(Hong Kong)