Product Summary

The EPF10K20RC240-3 is an embedded programmable logic device. With up to 250,000 gates, the FLEX 10K family provides the density, speed, and features to integrate entire systems, including multiple 32-bit buses, into a single device. No special design technique was required to implement the applications; the designer simply inferred or instantiated a function in a Verilog HDL, VHDL, Altera Hardware Description Language (AHDL), or schematic design file.

Parametrics

EPF10K20RC240-3 absolute maximum ratings: (1)Supply voltage: -2.0 to 7.0 V; (2)DC input voltage: -2.0 to 7.0 V; (3)DC output current, per pin: –25 to 25 mA; (4)Storage temperature No bias: -65 to 150 ° C; (5)Ambient temperature Under bias:–65 to 135 ° C; (6)Junction temperature: +150 °C.

Features

EPF10K20RC240-3 features: (1)High-performance, EEPROM-based programmable logic devices (PLDs) based on second-generation MAXR architecture; (2)5.0-V in-system programmability (ISP) through the built-in IEEE Std. 1149.1 Joint Test Action Group (JTAG) interface available in AX 7000S devices; (3)ISP circuitry compatible with IEEE Std. 1532; (4)Includes 5.0-V MAX 7000 devices and 5.0-V ISP-based MAX 7000S devices; (5)Built-in JTAG boundary-scan test (BST) circuitry in MAX 7000S devices with 128 or more macrocells; (6)Complete EPLD family with logic densities ranging from 600 to 5,000 usable gates (see Tables 1 and 2); (7)5-ns pin-to-pin logic delays with up to 175.4-MHz counter frequencies (including interconnect); (8)PCI-compliant devices available; (9)Open-drain output option in MAX 7000S devices; (10)Programmable macrocell flipflops with individual clear, preset, clock, and clock enable controls; (11)Programmable power-saving mode for a reduction of over 50% in each macrocell; (12)Configurable expander product-term distribution, allowing up to 32 product terms per macrocell; (13)44 to 208 pins available in plastic J-lead chip carrier (PLCC), ceramic pin-grid array (PGA), plastic quad flat pack (PQFP), power quad flat pack (RQFP), and 1.0-mm thin quad flat pack (TQFP) packages; (14)Programmable security bit for protection of proprietary designs; (15)3.3-V or 5.0-V operation.

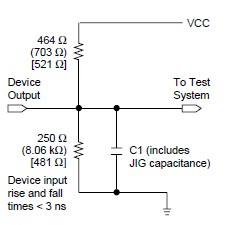

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

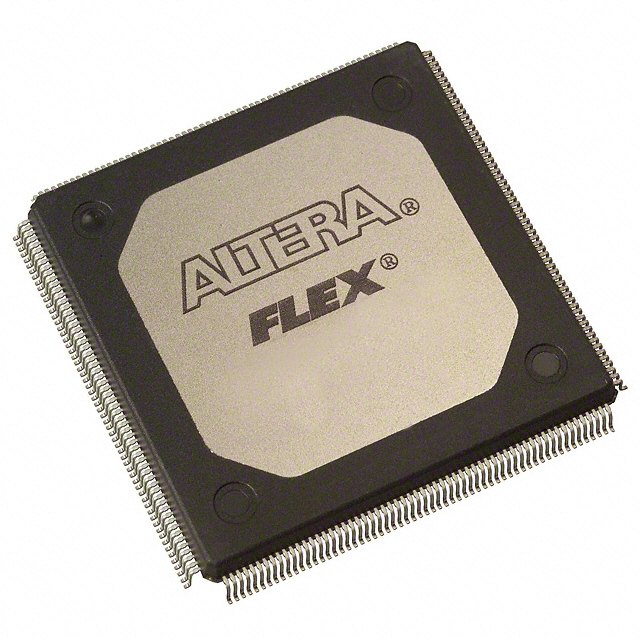

EPF10K20RC240-3 |

|

IC FLEX 10K FPGA 20K 240-RQFP |

Data Sheet |

|

|

||||||

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||

|

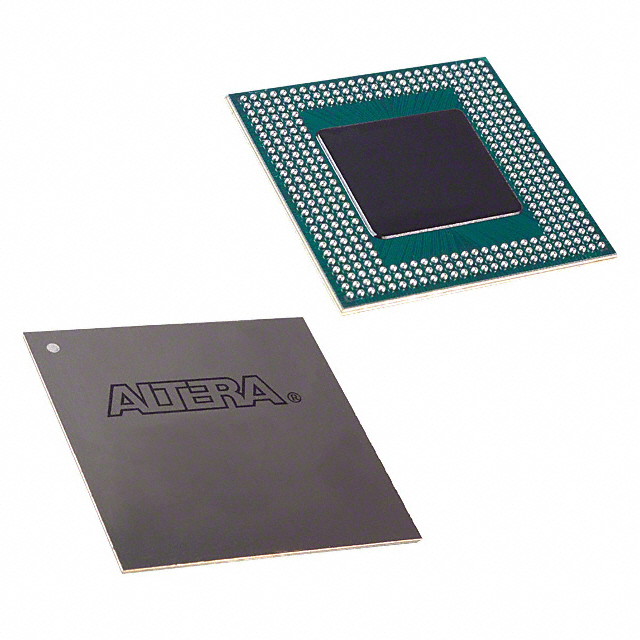

EPF10K100ABC356-2 |

|

IC FLEX 10KA FPGA 100K 356-BGA |

Data Sheet |

|

|

||||||

|

EPF10K100ABC356-2N |

|

IC FLEX 10KA FPGA 100K 356-BGA |

Data Sheet |

|

|

||||||

|

EPF10K100ABC356-3 |

|

IC FLEX 10KA FPGA 100K 356-BGA |

Data Sheet |

|

|

||||||

|

EPF10K100ABI600-2 |

|

IC FLEX 10KA FPGA 100K 600-BGA |

Data Sheet |

|

|

||||||

|

EPF10K100ARC240-1 |

|

IC FLEX 10KA FPGA 100K 240-RQFP |

Data Sheet |

|

|

||||||

|

EPF10K100ARC240-1N |

|

IC FLEX 10KA FPGA 100K 240-RQFP |

Data Sheet |

|

|

||||||

(Hong Kong)

(Hong Kong)